Codasip offers its tools and IP for free to academic institutions and universities.

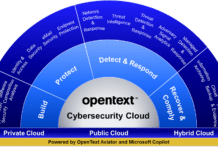

Codasip, a RISC-V Custom Compute startup, has announced that it has achieved certification for the functional safety standard ISO 26262 and the cybersecurity engineering standard ISO/SAE 21434. These certifications were awarded by TÜV SÜD, confirming that Codasip’s IP hardware engineering development processes, guidelines, and work instructions meet the rigorous requirements of these standards.

The certified processes are currently being used by Codasip’s engineering team in the development of new automotive IP products. This adherence to standardised processes provides a solid foundation for streamlined and efficient IP product compliance and assessments.

Codasip is a Czech-German startup that began around 10 years ago in Brno, Czech Republic. It has design centres across Europe, including in France, Spain, Germany, and the United Kingdom. They also have sales representatives worldwide.

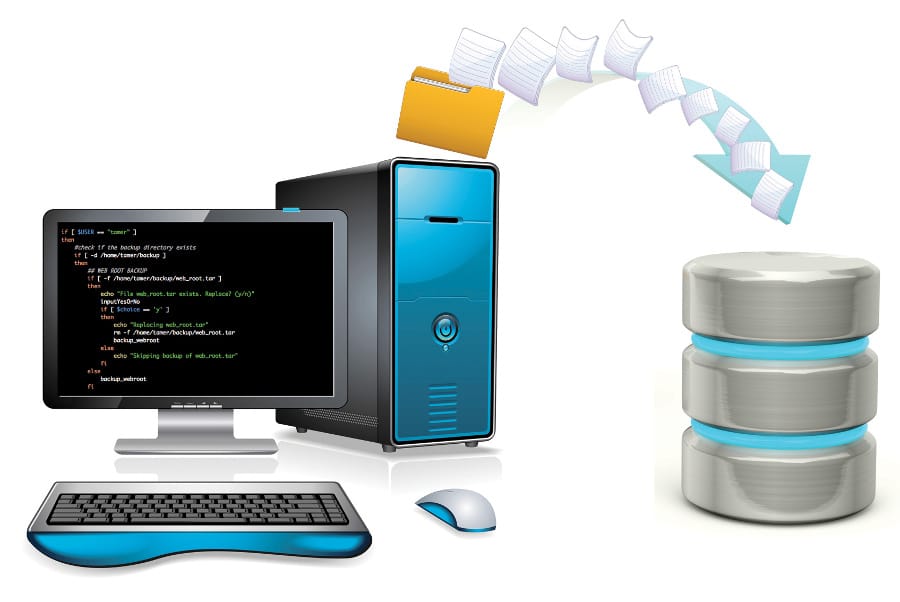

The company provides intellectual property (IP) for RISC-V processors, IP Pro. This means they create digital designs for processors that can be used by other companies in their products. These designs are written in hardware description languages like Verilog or VHDL.

They also provide a tool, Studio, that allows developers to create CPUs using a high-level, C-like language. This tool is not limited to RISC-V processors but is particularly well-suited for them. Studio enables customisation and quick iteration in processor design. It enables developers to define the processor’s architecture, simulate its performance, and generate the necessary hardware description files.

Codasip offers its tools and IP for free to academic institutions and universities. This program allows students and researchers to learn and experiment with industry-standard tools while providing Codasip with access to new ideas and innovations from academia.

Codasip is working on various aspects of processor technology, including functional safety, security, acceleration, graphics, in-memory processing, low-power solutions, and high-performance architectures like out-of-order execution.