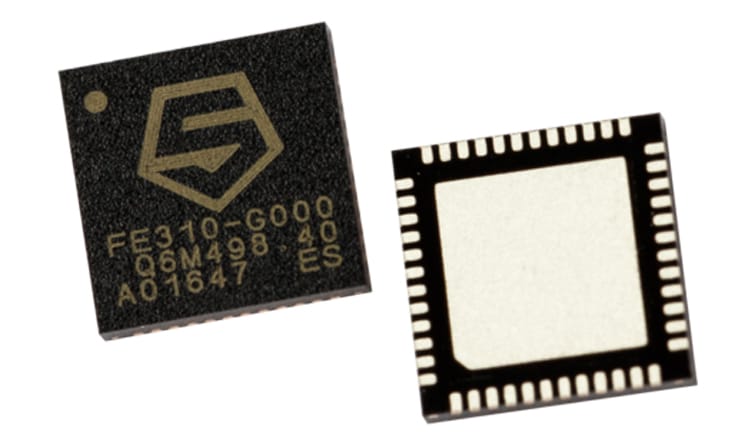

SiFive has announced the industry’s first open source SoC based on RISC-V instruction set architecture, called Freedom Everywhere 310 (FE310). The company is also working on developing low-cost HiFive1 software development board that works with the new chip.

The FE310 features E41 CPU Coreplex, 32-bit RV32IMAC with clock-speed of 320+ MHz. It offers 16KB L1 instruction cache memory, 16KB Data SRAM scratchpad, hardware multiply/divide option, debug module and one-time programmable non-volatile memory. The chip is used to power HiFive1 that debuts as the latest Arduino-compatible board.

The HiFive1 is targeted at software developers, hackers and system architects who want to experience RISC-V and build their own microcontroller. The board has a microUSB port as a host interface to enable programming and debugging on the open source chip.

Alongside the FE310 chip and HiFive1 development board, SiFive has published its register-transfer level (RTL) code. The company is seeking the support of open source community to take the present development to the next level.

SiFive has a long-term vision for supporting open source semiconductors. The contribution of FE310 RTL code will encourage the open spruce community to develop support for RISC-V and other hardware development.